**Product Specification 1001.549701** Issue Date 04 April 2019 08:13:4

| Part Number Customer |           |                                                 |                                      |                                        |  |

|----------------------|-----------|-------------------------------------------------|--------------------------------------|----------------------------------------|--|

| Category             | Parameter |                                                 | Specification                        | Measurement Method                     |  |

| OverallWafer         | 1.0       | Diameter                                        | 150.00 +/- 0.50 mm                   | Wafer Vendor                           |  |

|                      | 2.0       | Primary Flat Orientation                        | {110}+/-0.5 degree                   | Wafer Vendor                           |  |

|                      | 3.0       | Primary Flat Length                             | 57.50 +/- 2.50 mm                    | Wafer Vendor                           |  |

|                      | 4.0       | Secondary Flat Orientation                      | none                                 |                                        |  |

|                      | 5.0       | Edge Rounding                                   | Semi M1                              | Wafer Vendor                           |  |

|                      | 6.0       | Overall Thickness                               | 511.00 +/- 6.00 μm                   | ADE, 100%                              |  |

|                      | 7.0       | Total Thickness Variation (TTV)                 | <3.00μm                              | Guaranteed by Process                  |  |

|                      | 8.0       | Global Flatness (TIR)                           | <3.00um                              | ADEmeasurement 100%                    |  |

|                      | 9.0       | Bow                                             | <100.00μm                            | ADE to ASTM F534, 20%                  |  |

|                      | 10.0      | Warp                                            | <100.00μm                            | ADE to ASTM F657, 20%                  |  |

|                      | 11.0      | Edge Chips                                      | 0                                    | Bright Light, 100% (note 2)            |  |

|                      | 12.0      | Edge Exclusion                                  | 5mm                                  |                                        |  |

| HandleSilicon        | 13.0      | Handle Growth Method                            | CZ                                   | Wafer Vendor                           |  |

|                      | 14.0      | Handle Orientation                              | {100} +/- 1 degree                   | Wafer Vendor                           |  |

|                      | 15.0      | Handle Doping Type                              | Any                                  | Wafer Vendor                           |  |

|                      | 16.0      | Handle Dopant                                   | Any                                  | Wafer Vendor                           |  |

|                      | 17.0      | Handle Resistivity                              | >1 Ohmcm                             | Wafer Vendor                           |  |

|                      | 18.0      | Handle Thickness                                | 500.00 +/- 5.00 um                   | ADE, 100%inspection                    |  |

|                      | 19.0      | Backside Finish                                 | Lapped with oxide and laserwith mask | Guaranteed by Process                  |  |

| BuriedOxide          | 24.0      | Oxide Type                                      | Thermal                              | Guaranteed by process                  |  |

|                      | 25.0      | Oxide formed on                                 | Device and handle wafers             | Guaranteed by process                  |  |

|                      | 26.0      | Oxide Thickness                                 | 10,000.00 +/- 500.00 A               | Nanospec centre point, 4%              |  |

| DeviceSilicon        | 33.0      | Device Growth Method                            | CZ                                   | Wafer Vendor                           |  |

|                      | 34.0      | Device Orientation                              | {100} +/- 0.5 degree                 | Wafer Vendor                           |  |

|                      | 35.0      | Device Doping Type                              | N                                    | Wafer Vendor                           |  |

|                      | 36.0      | Device Dopant                                   | Phosphorous                          | Wafer Vendor                           |  |

|                      | 37.0      | Device Resistivity                              | 1 - 3 Ohmem                          | Wafer Vendor                           |  |

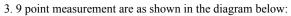

|                      | 38.0      | Nominal Thickness                               | 9.50 +/- 0.75 um                     | FTIR or Filmetrics 9 point measurement |  |

|                      | 39.0      | Distance to device silicon edge from wafer edge | <2mm                                 | Guaranteed by process                  |  |

|                      | 40.0      | Surface                                         | roughness < 3A rms                   | Guaranteed by process                  |  |

|                      | 41.0      | Voids                                           | none inside 5mm edge exclusion       | Bright Light inspection 100%           |  |

|                      | 42.0      | Scratches                                       | none                                 | Bright Light inspection 100%           |  |

|                      | 43.0      | Haze                                            | none                                 | Bright Light inspection                |  |

|                      | 44.0      | Device Field Oxidation                          | 5,000.00 +/- 250.00 A                | Nanospec centre point, 4%              |  |

Icemos Technology Ltd

| Part Number       |                                                                                                                | Customer                                                                                |                    |  |

|-------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|--|

| Category          | Parameter                                                                                                      | Specification                                                                           | Measurement Method |  |

| Shipping Details  | Wafer per box :                                                                                                | Max 25                                                                                  |                    |  |

|                   | Packaging:                                                                                                     | Taped Polypropylene Wafer Box<br>Empak, Ultrapak, 150.00mm<br>Antistatic Double Bagging |                    |  |

|                   | Lot Shipment Data                                                                                              | Device Thickness Bow / Warp Data Handle and SOI Thickness                               |                    |  |

| Explanatory Notes | 1. Microscope inspec                                                                                           | tion performed using microscope scan as below. 5x objective.                            |                    |  |

|                   | 2. All bright light inspections performed exclude all wafer area outside the edge exclusion defined in Overall |                                                                                         |                    |  |

2. All bright light inspections performed exclude all wafer area outside the edge exclusion defined in Overall Wafer, Edge Exclusion. High intensity bright lamp inspection as per ASTM F523.

Additional Information