# ICE//OS Technology

### Engineered Silicon Substrates Selector Guide

Ver.5 EN 2025

IceMOS Technology

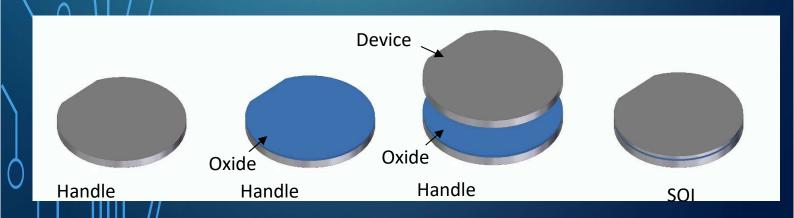

### SOI Solutions

#### **Applications**

Our customised SOI solutions are used in the following fields:

- Advanced pressure sensors

- Accelerometers

- Gyroscopes

- Microfluidics/flow sensors

- RF MEMS

- MOEMs/Optical MEMs

- Optoelectronics

- Smart Power

- Advanced Analog ICs

- Microphones

- Luxury watches

#### End Markets:

- Telecommunications

- Medical

- Automotive

- Consumer

- Instrumentation

with <1.5mm edge terrace

We have extensive experience in a variety of SOI substrates and our highly skilled applications engineering team is available to assist you to select the optimum combination of parameters for your requirements, ensuring that you receive the perfect custom SOI solution for your application.

By making continuous improvements to our processes in a Lean Six Sigma environment, IceMOS Technology offer world class product quality, competitive cost structure plus rapid turnaround makes IceMOS Technology your ideal SOI partner.

#### **SOI Specification**

| Pai                         | rameter                                  | Specification Range                              |             |  |  |

|-----------------------------|------------------------------------------|--------------------------------------------------|-------------|--|--|

| Wa                          | fer Diameter                             | 100, 125, 150<br>mm                              | 200 mm      |  |  |

| Ha                          |                                          |                                                  |             |  |  |

| Ha                          | ndle Thickness                           | 200-1100 µm                                      | 450-1100 μm |  |  |

| Tol                         | ndle Thickness<br>lerance                | ±5 μm                                            |             |  |  |

| Sta                         | ack Thickness                            | 280-1150 μm<br>N or P                            |             |  |  |

| Do                          | pant Type                                |                                                  |             |  |  |

| Do                          | ping                                     | N type: Phos, Red Phos, Sb & As<br>P type: Boron |             |  |  |

| Re                          | sistivity                                | ≤0.001 - ≥10000 Ω-cm                             |             |  |  |

| Gro                         | owth Method                              | CZ, MCZ or FZ                                    |             |  |  |

| Cry                         | vstal Orientation                        | <100>, <111> or <110>                            |             |  |  |

| Ba                          | ckside Finish                            | Lapped/Etched or Polished                        |             |  |  |

| Bu                          | ried Oxide Specification                 | S                                                |             |  |  |

|                             | ermally Oxidised<br>ried Oxide Thickness |                                                  |             |  |  |

| Device Layer Specifications |                                          |                                                  |             |  |  |

| De                          | vice Layer Thickness                     | ≥1.5 µm                                          | ≥5 μm       |  |  |

| Tol                         | lerance                                  | ± 0.5 μm                                         | ±0.8 μm     |  |  |

| Do                          | pant Type                                | N or P                                           |             |  |  |

| Do                          | ping                                     | N type: Phos, Red Phos, Sb & As<br>P type: Boron |             |  |  |

| Re                          | sistivity                                | ≤0.001 <sup>–</sup> ≥10000 Ω-cm                  |             |  |  |

| Gro                         | owth Method                              | CZ, MCZ or FZ                                    |             |  |  |

| Cry                         | vstal Orientation                        | <100>, <111> or <110>                            |             |  |  |

| Bu                          | ried Layer Implant                       | N type or P type                                 |             |  |  |

|                             |                                          |                                                  |             |  |  |

## SiSi Solutions

#### Applications

- High Voltage PIN Diodes

- RF Attenuators

- Photo Detectors

- ✓ X-Ray Detectors

- IR Sensors

- HV Power Devices

- Replacement for Epitaxial layers

#### **Key Features:**

- High Quality

- Low cost

- Low defect density

- Excellent Layer uniformity

- Multiple layers

- Sharp transitions

- Layer resistivity up to 10kΩ-cm

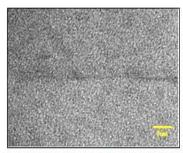

- Excellent interface quality verified by high resolution SAM Inspection

For semiconductor device manufacturers, the IceMOS Silicon – Silicon Direct bonded wafer offers a cost effective alternative to thick epitaxial layers and inverse epi that have traditionally been used for applications such as power devices and PiN diodes.

The use of direct wafer bonding technology allows silicon substrates to be produced containing multiple layers of single crystal silicon. These layers can have a resistivity range  $1m\Omega$ -cm to  $10k\Omega$ -cm, N and P-type and can include combinations of orientations – a feature not possible with conventional epitaxial wafers.

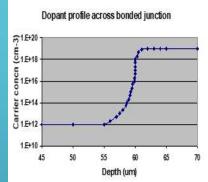

The IceMOS SiSi bonding process gives a high quality wafer with low leakage, low warp and a low defect density. Additionally, the thickness variation in the layers can be as little as +/-0.5um. The transition between high and low dopant levels can be sharp or soft, depending on the application or customer requirement.

High resolution TEM image of SiSi wafer interface

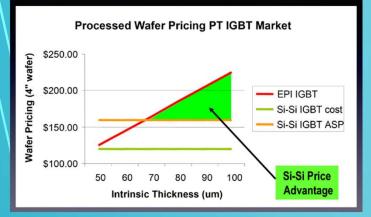

shows This chart the cost advantage of SiSi direct wafer bonding over Epi layers as a starting for material many electronic devices. This makes SiSi wafers an advantageous option for performance and cost reduction.

#### SiSi Specification

| Parameter                         | Specification Ra                                                            | Specification Range |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------------|---------------------|--|--|--|

| Wafer Diameter                    | 100, 125, 150<br>mm                                                         | 200 mm              |  |  |  |

| Handle Layer Specification        | าร                                                                          |                     |  |  |  |

| Handle Thickness                  | 200-1100 μm                                                                 | 450-1100 μm         |  |  |  |

| Handle Thickness<br>Tolerance     | ±5 μm                                                                       | ±5 μm               |  |  |  |

| Stack Thickness                   | 280-1150 μm                                                                 | 280-1150 μm         |  |  |  |

| Dopant Type                       | N or P                                                                      | N or P              |  |  |  |

| Doping                            | N type: Phos, Red Phos, Sb & As<br>P type: Boron                            |                     |  |  |  |

| Resistivity                       | ≤0.001 <sup>–</sup> ≥10000 Ω-cm                                             |                     |  |  |  |

| Growth Method                     | CZ, MCZ or FZ                                                               |                     |  |  |  |

| Crystal Orientation               | <100>, <111> or <110>                                                       |                     |  |  |  |

| Backside Finish                   | Lapped/Etched or Polished                                                   |                     |  |  |  |

| <b>Device Layer Specification</b> | 5                                                                           |                     |  |  |  |

| Device Layer Thickness            | ≥20 µm                                                                      | ≥20 µm              |  |  |  |

| Tolerance                         | ± 0.5 μm                                                                    | ±0.8 μm             |  |  |  |

| Dopant Type                       | N or P                                                                      |                     |  |  |  |

| Doping                            | N type: Phos, Red Phos, Sb & As<br>P type: Boron                            |                     |  |  |  |

| Resistivity                       | ≤0.001 <sup>–</sup> ≥10000 Ω-cm                                             |                     |  |  |  |

| Growth Method                     | CZ, MCZ or FZ                                                               |                     |  |  |  |

| Crystal Orientation               | <100>, <111> or <110>                                                       |                     |  |  |  |

| Buried Layer Implant              | N type or P type<br>becification; however, we are always happy to work with |                     |  |  |  |

our customers to engineer specific solutions. If you would like to discuss an alternative specification, please contact our sales team: sales@icemostech.com

# Cooler than Cool

### **DSOI** Solutions

#### Applications

Our customised Double SOI (DSOI) solutions are used in the following fields:

- SOI solutions for MEMS/MST

- Microfluidics/flow sensors

- RF MEMS

- MOEMs

- Optoelectronics

- Optical MEMS

#### End Markets:

- Telecommunications

- Medical

- Automotive

- Consumer

- Security

IceMOS Technology is a leading supplier of Double or Multi-Layer SOI for a large range of IC and MEMS applications. With over 20 years' experience in SOI manufacturing, we offer an impressive specification range, which is amongst the widest available in the market, ensuring that you receive the perfect DSOI solution for your application. We have extensive experience in SOI substrates, and our applications engineering expertise can help you select the best combination of parameters to aid your downstream processing of the DSOI engineered substrate.

With a flexible approach, IceMOS allows the customer to grow from R&D production (offering small lots) to volume production. Our experienced MEMS process engineers have experience in optical, inertial, and other MEMS fields. IceMOS Technology offer additional foundry processing for MEMS, trench isolation, buried cavity, layer release, etc.

By making continuous improvements to our processes in a Lean Six Sigma environment, IceMOS Technology offer world class product quality, competitive cost structure plus rapid turnaround makes IceMOS Technology your ideal DSOI partner.

#### **DSOI** Specification

| Parameter                                    | meter Specification Range                              |                                       |  |  |  |

|----------------------------------------------|--------------------------------------------------------|---------------------------------------|--|--|--|

| Wafer Diameter                               | 100, 125, 150<br>mm                                    | 200 mm                                |  |  |  |

| Handle Layer Specifications                  |                                                        |                                       |  |  |  |

| Handle Thickness                             | 200-1100 μm                                            | 450-1100 μm                           |  |  |  |

| Handle Thickness<br>Tolerance                | ±5 μm                                                  |                                       |  |  |  |

| Stack Thickness                              | 280-1150 μm                                            |                                       |  |  |  |

| Dopant Type                                  | N or P                                                 |                                       |  |  |  |

| Doping                                       | N type: Phos, Red Phos, Sb & As<br>P type: Boron       |                                       |  |  |  |

| Resistivity                                  | ≤0.001 <sup>–</sup> ≥10000 Ω-cm                        |                                       |  |  |  |

| Growth Method                                | CZ, MCZ or FZ                                          |                                       |  |  |  |

| Crystal Orientation                          | <100>, <111> or <110>                                  |                                       |  |  |  |

| Backside Finish                              | Lapped/Etched or Polished                              |                                       |  |  |  |

| <b>Buried Oxide Specificatio</b>             | Buried Oxide Specifications                            |                                       |  |  |  |

| Thermally Oxidised<br>Buried Oxide Thickness | 0.2 – 4.0 μm grown on Handle, Device or<br>both wafers |                                       |  |  |  |

| <b>Device Layer Specificatio</b>             | ns (1 <sup>st</sup> and 2 <sup>nd</sup> Lay            | er)                                   |  |  |  |

| Device Layer Thickness                       | ≥1.5 μm                                                | ≥5 μm                                 |  |  |  |

| Tolerance                                    | ± 0.5 μm and ±<br>1 μm                                 | $\pm 0.8~\mu m$ and $\pm$ 1.6 $\mu m$ |  |  |  |

| Dopant Type                                  | N or P                                                 |                                       |  |  |  |

| Doping                                       | N type: Phos, Red Phos, Sb & As<br>P type: Boron       |                                       |  |  |  |

| Resistivity                                  | ≤0.001 - ≥10000 Ω-cm                                   |                                       |  |  |  |

| Growth Method                                | CZ, MCZ or FZ                                          |                                       |  |  |  |

| Crystal Orientation                          | <100>, <111> or <110>                                  |                                       |  |  |  |

| Buried Layer Implant                         | N type or P type                                       |                                       |  |  |  |

|                                              |                                                        |                                       |  |  |  |

### **DSP Solutions**

#### Applications

Our customised Double-Sided Polished substrates are used in the following fields:

- DSP solutions for MEMS/MST

- Microfluidics/flow sensors

- RF MEMS

- Optoelectronics

#### **End Markets:**

- Telecommunications

- Medical

- Automotive

- Consumer

- Security

IceMOS uses over 20 years of experience to offer the marketplace world class custom DSP solutions (Double Sided Polished).

Our highly skilled team has many years of design and manufacturing experience to help develop a DSP solution to your requirement.

IceMOS DSP wafers are an excellent substrate for double sided lithography processing; the IceMOS expertise and knowledge of the product and the allow for processes exceptional thickness control and surface roughness - ideal for a downstream wafer bonding process. Additionally, specifications non-standard for demanding applications will always be considered.

Our world class product quality, competitive cost structure plus rapid turnaround makes IceMOS Technology your ideal DSP partner.

#### **DSP Specification**

| Parameter                                   | Specification Range                              |             |  |

|---------------------------------------------|--------------------------------------------------|-------------|--|

| Wafer Diameter                              | 100, 125, 150mm                                  | 200mm       |  |

| Wafer Thickness                             | 300-1150 μm                                      | 450-1150 μm |  |

| Wafer Thickness Tolerance                   | ±2 μm                                            | ±5 μm       |  |

| Total Thickness Variation<br>(TTV)          | ≤1 μm                                            | ≤2 μm       |  |

| Bow                                         | ≤40 μm                                           |             |  |

| Warp                                        | ≤40 μm                                           |             |  |

| Roughness                                   | ≤2Å                                              |             |  |

| Dopant Type                                 | N or P                                           |             |  |

| Doping                                      | N type: Phos, Red Phos, Sb & As<br>P type: Boron |             |  |

| Resistivity                                 | ≤0.001 - ≥10000 Ω-cm                             |             |  |

| Growth Method                               | CZ, MCZ or FZ                                    |             |  |

| Crystal Orientation                         | <100>, <111> or <110>                            |             |  |

| Thermally Oxidised Field<br>Oxide Thickness | 0.2-4.0 μm                                       |             |  |

# Cooler than Cool

#### Applications

Our customised SOI solutions are used in the following fields:

- Advanced pressure sensors

- Inertial MEMS

- Microfluidics

- Resonators

- Microphones

#### End Markets:

- Telecommunications

- Medical

- Automotive

- Consumer

- Instrumentation

IceMOS Technology is a leading supplier of 100-150mm Cavity Bonded SOI wafers for a large range of MEMS applications. By utilising years of deep silicon trench etch expertise and experience coupled with our advanced wafer bonding technology allow customer cavity expectations to be materialized into innovative products.

The IceMOS Cavity Bonded SOI is a preetched feature embedded under a silicon membrane. This provides an opportunity for the customer designers to develop more intelligent devices to meet the most demanding markets.

Our Cavity Bonded SOI solutions allow the customer to take advantage of –

- IceMOS' superior bonding technology and expertise.

- Reduce any stiction issues at release.

- Simplified manufacturing flows.

- Low Cost Cavity SOI/Si-Si Solutions.

- Flexibility in construction around customer needs/ downstream applications.

IceMOS can offer various methods of constructing the Cavity Bonded SOI Solutions to optimize customer cavity requirements. C-SAM and AVI inspection can be included as desired.

We also have the added advantage of incorporating advanced features into Cavity Bonded SOI solutions which potentially opens possibilities that might otherwise not have been considered.

Cavity Handle With Oxide Handle Courte Autore Cavity Handle Handle Courte Autore Cavity Handle Handle Cavity Handle Handle Cavity Handle Handle Cavity Handle With Oxide Handle Cavity Handle With Oxide Handle Cavity Handle Handle Cavity Handle Hand

**CAVITY SOI WAFERS**

| Cooler than Coo                              | https://www.icemostech.com/                            |  |  |  |

|----------------------------------------------|--------------------------------------------------------|--|--|--|

|                                              |                                                        |  |  |  |

| CSOI Specification                           |                                                        |  |  |  |

| Parameter                                    | Specification Range                                    |  |  |  |

| Wafer Diameter                               | 100, 125, 150 mm                                       |  |  |  |

| landle Layer Specifications                  |                                                        |  |  |  |

| Handle Thickness                             | 200–1100 μm                                            |  |  |  |

| Handle Thickness<br>Tolerance                | ±5 μm                                                  |  |  |  |

| Stack Thickness                              | 280-1150 μm                                            |  |  |  |

| Dopant Type                                  | N or P                                                 |  |  |  |

| Doping                                       | N type: Phos, Red Phos, Sb & As<br>P type: Boron       |  |  |  |

| Resistivity                                  | ≤0.001 - ≥10000 Ω-cm                                   |  |  |  |

| Growth Method                                | CZ, MCZ or FZ                                          |  |  |  |

| Crystal Orientation                          | <100>, <111> or <110>                                  |  |  |  |

| Backside Finish                              | Lapped/Etched or Polished                              |  |  |  |

| <b>Buried Oxide Specification</b>            | S                                                      |  |  |  |

| Thermally Oxidised Buried<br>Oxide Thickness | 0.2 – 4.0 µm grown on Handle, Device or<br>both wafers |  |  |  |

| <b>Device Layer Specifications</b>           | 5                                                      |  |  |  |

| Device Layer Thickness                       | ≥1.5 μm                                                |  |  |  |

| Tolerance                                    | ± 0.5 μm                                               |  |  |  |

| Dopant Type                                  | N or P                                                 |  |  |  |

| Doping                                       | N type: Phos, Red Phos, Sb & As<br>P type: Boron       |  |  |  |

| Resistivity                                  | ≤0.001 - ≥10000 Ω-cm                                   |  |  |  |

| Growth Method                                | CZ, MCZ or FZ                                          |  |  |  |

| Crystal Orientation                          | <100>, <111> or <110>                                  |  |  |  |

| Buried Layer Implant                         | N type or P type                                       |  |  |  |

| Membrane Thickness/SOI<br>Thickness          | >2 µm                                                  |  |  |  |

| Membrane Tolerance                           | +/-0.5 μm                                              |  |  |  |

| Cavity Span: Membrane<br>Thickness           | <50:1 µm (dependent on design)                         |  |  |  |

|                                              |                                                        |  |  |  |

**Minimum Bonding Size** 20 µm Features Alignment Accuracy of +/-3 μm **Cavity to Alignment Marks** 1-30 µm @ +/-10% **Cavity Depth** 31-300 µm @ +/-20% Handle, Device or Buried Oxide **Cavity Location**

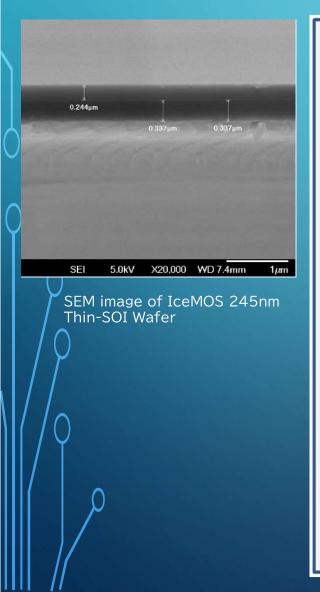

### **Thin-SOI Solutions**

#### Applications

Our customised Thin-SOI solutions are suitable for the following fields:

- •RF Filters

- Optoelectronics

- •Image Sensing

- Wireless Connectivity

- •Flexible-Hybrid Electronics

- •RF MEMS

#### End Markets:

Telecommunications

- •Consumer

- •Power

- Medical

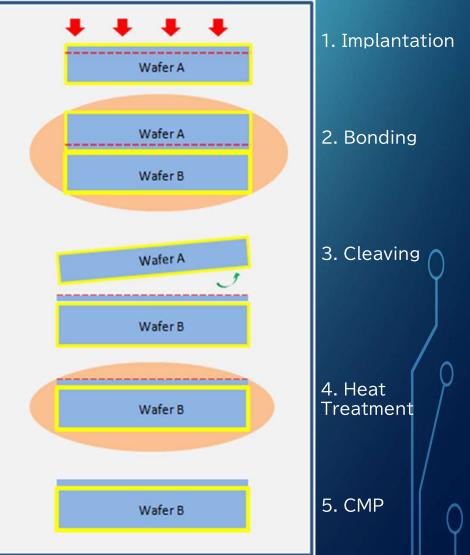

IceMOS Technology has developed and is offering a Thin-SOI wafer range with device layers <  $1\mu$ m. Building on the 20+ years of SOI manufacturing experience, IceMOS is offering the same high-quality product as our existing Thick-SOI wafers for RF Applications.

With the wide range of specifications for both silicon wafers and the thermally grown Buried Oxide Layer, the IceMOS Thin-SOI wafer range covers applications such as Silicon Photonics to SAW filters.

By making continuous improvements to our processes in a Lean Six Sigma environment, IceMOS Technology offer world class product quality, competitive cost structure plus rapid turnaround makes IceMOS Technology your ideal SOI partner.

#### **Thin-SOI Specification**

| Parameter                                    | Specification Range                           |  |  |  |

|----------------------------------------------|-----------------------------------------------|--|--|--|

| Wafer Diameter                               | 150 - 200 mm                                  |  |  |  |

| Handle Layer Specifications                  | S                                             |  |  |  |

| Dopant Type                                  | N or P                                        |  |  |  |

| Doping                                       | N type: Phos, Sb & As<br>P type: Boron        |  |  |  |

| Resistivity                                  | ≤0.001 <sup>–</sup> ≥10000 Ω-cm               |  |  |  |

| Growth Method                                | CZ, MCZ or FZ                                 |  |  |  |

| <b>Buried Oxide Specifications</b>           | 5                                             |  |  |  |

| Thermally Oxidised Buried<br>Oxide Thickness | 0.1um – 2µm grown on Device or both<br>wafers |  |  |  |

| Buried Oxide Uniformity                      | ± 5%                                          |  |  |  |

| Device Layer Specifications                  |                                               |  |  |  |

| Device Layer Thickness                       | 0.1um - 1um                                   |  |  |  |

| Device Layer Uniformity                      | ± 20nm                                        |  |  |  |

| Dopant Type                                  | N or P                                        |  |  |  |

| Doping                                       | N type: Phos, Sb & As<br>P type: Boron        |  |  |  |

| Resistivity                                  | ≤0.001 <sup>–</sup> ≥10000 Ω-cm               |  |  |  |

| Growth Method                                | CZ, MCZ or FZ                                 |  |  |  |

| Crystal Orientation                          | <100>, <111> or <110>                         |  |  |  |

#### **Applications**

- MEMS devices

- Solid State Relay photovoltaic generators

- Photovoltaic cells and

- Optoelectronic devices/ICs

- High Voltage Analog ICs for

- telecommunications

- High performance bipolar circuits

- U Smart Power ICs

- Integrated Sensors

#### **Key Features:**

- Complete device isolation

- Allows significant die shrinkage compared with conventional Junction isolation

- Much lower defect density than conventional DI technologies

- Lower Substrate capacitance

than bulk

- Lower cost than trench isolation on epi

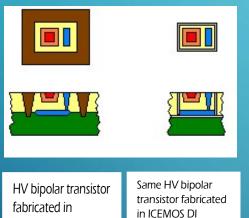

Junction isolated IC technology Illustration shows a comparison of HV bipolar IC transistors made on junction

isolated and ICEMOS DI technologies, showing 3x saving in silicon real estate. https://www.icemostech.com/

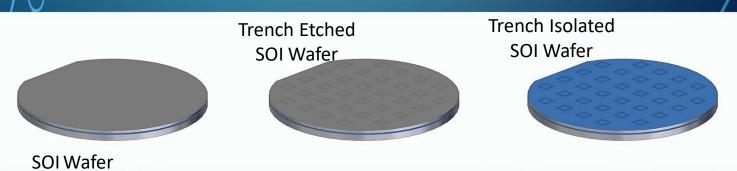

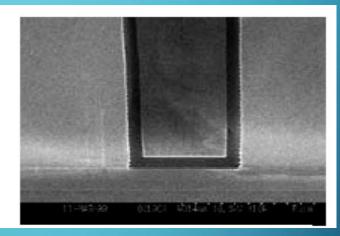

## Trench SOI

IceMOS Technology presents its dielectric isolation technology – delivering high voltage isolation between components on the same chip. Isolation is achieved using thick film SOI technology combined with state-of-the-art high aspect ratio deep trench etching and oxide/poly refill. This technology is available on all wafer sizes from 100mm to 150mm and silicon device layers from 1.5um to 100um.

#### Supply Options Available

- Provision of DI Substrate from isolation mask provided

- Provision of Fully processed DI IC using ICEMOS as foundry to complete post isolation processing

- Provision of Full IC design and fabrication on DI from customer schematic

#### Post Isolation technologies available

- Simple Bipolar

- CMOS (1P, 2M)

- BiCMOS (1P, 2M)

#### The IceMOS trench-isolated silicon-oninsulator (SOI) substrate provides complete dielectric isolation of tubs.

- Key benefits are:

- Elimination of buried layer

- Elimination of epi layer

- Elimination of P+ isolation diffusion

- Minimizing of parasitic capacitances

- High quality crystalline silicon layer

- Simultaneous increase of die per wafer

- High voltage breakdown capability

- Customised trench patterns

Our process engineers will work closely with your design group to realize the full potential for your processes.

#### **Trench SOI Specification**

| Parameter                                    | Specification Range                                 |

|----------------------------------------------|-----------------------------------------------------|

| Wafer Diameter                               | 100, 125, 150 mm                                    |

| Handle Layer Specifications                  |                                                     |

| Handle Thickness                             | 350-800 μm                                          |

| Handle Thickness Tolerance                   | ±5 μm                                               |

| Stack Thickness                              | 350-1150 μm                                         |

| Dopant Type                                  | N or P                                              |

| Doping                                       | N type: Phos, Red Phos, Sb & As<br>P type: Boron    |

| Resistivity                                  | ≤0.001 <sup>–</sup> ≥10000 Ω-cm                     |

| Growth Method                                | CZ, MCZ or FZ                                       |

| Crystal Orientation                          | <100>, <111> or <110>                               |

| Backside Finish                              | Lapped/Etched or Polished                           |

| Buried Oxide Specifications                  |                                                     |

| Thermally Oxidised Buried<br>Oxide Thickness | 0.2 – 4.0 µm grown on Handle, Device or both wafers |

| Device Layer Specifications                  |                                                     |

| Device Layer Thickness                       | 1.5 - 100 μm                                        |

| Tolerance                                    | ± 0.5 μm                                            |

| Dopant Type                                  | N or P                                              |

| Doping                                       | N type: Phos, Red Phos, Sb & As<br>P type: Boron    |

| Resistivity                                  | ≤0.001 <sup>–</sup> ≥10000 Ω-cm                     |

| Growth Method                                | CZ, MCZ or FZ                                       |

| Crystal Orientation                          | <100>, <111> or <110>                               |

| Buried Layer Implant                         | N type or P type                                    |

| Trench Mask Tone                             | Positive Resist                                     |

| Trench Mask Type                             | E-beam master for projection aligner                |

| Trench Line Width                            | > 2um                                               |

| Trench Aspect Ratio                          | 15:1                                                |

| Trench Sidewall Doping Type                  | Phosphorus                                          |

| Trench Refill – Oxide (each sidewall)        | 0.1 – 1.0 μm                                        |

| Trench Refill – Polysilicon                  | To Fill (Doped or undoped Polysilicon)              |

| Planarisation                                | СМР                                                 |

| Final Field Oxide                            | Thermal oxide + TEOS up to 1um                      |

|                                              |                                                     |

# Cooler than Cool

## **TSV Solutions**

Applications

Our customised Through Silicon Via solutions are used in the following fields:

- SOI solutions for MEMS/MST

- Microfluidics/flow sensors

- RF MEMS

- Optoelectronics

- Smart Power

- Advanced Analog ICs

#### End Markets:

- Telecommunications

- Medical

- Automotive

- Consumer

- Instrumentation

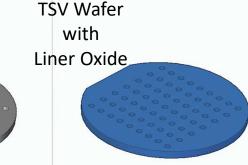

IceMOS Technology have developed an innovative and powerful through-wafer interconnect technology which can allow device designers in both standard IC and MEMS device industries overcome packaging problems associated with their designs. Using this interconnect solution allows many of our customers to migrate their designs easily to a wafer level package with solder bumped contacts.

The IceMOS Technology solution is a preprocessed substrate which is delivered to the customer with the interconnect already formed within the substrate. This substrate is fully CMOS compatible.

All interconnect is performed using through wafer etching and refill and heavily doped polysilicon. The wafers meet all standard specifications for surface metallic contamination, planarity and particle count. We have verified stable substrate performance up to diffusion temperatures of 1200C.

IceMOS will develop customer specific through-wafer interconnect solution in partner, taking the preferred interconnect pattern and implementing it on the wafer for easy connectivity to a circuit or sensor. The TSV may be beside or below existing bond pads. The design is optimised and fully customised to the customer's requirements.

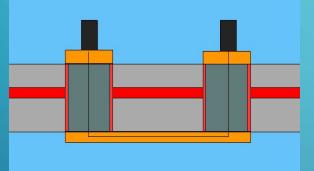

TSV Wafer

TSV Wafer with Polysilicon Interconnects

ICelVI

Cooler than Coo

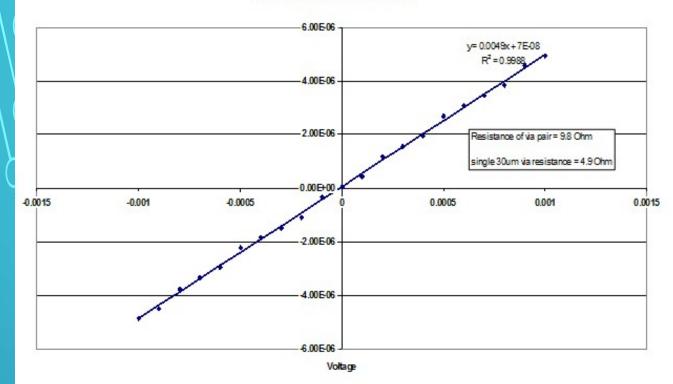

Vias directly connected top and bottom using Al-Si metallisation – no additional implants/diffusions. Characteristic shows completely Ohmic behaviour even at very low current levels.

#### **TSV Specification**

| Parameter             | Specification Range                          |

|-----------------------|----------------------------------------------|

| Aspect Ratio of Via   | <15:1                                        |

| Wafer Diameter        | 100mm & 150mm                                |

| Wafer Thickness       | 300-525µm                                    |

| Max. Diameter         | $40 \mu m$ on smallest side                  |

| Min. Pitch            | 90μm (3x via width)                          |

| Poly Resistivity      | <5 mΩ-cm                                     |

| Isolation Resistance  | Determined by oxide liner (design dependent) |

| Oxide Liner Thickness | 0.2-2µm                                      |

#### **Key Features:**

- High Quality

- $\bullet \cup$  Low cost

- Low defect density

ICEMOS

Cooler than Cool

- Multiple layers

- Process sequences specific to customer requirements can be offered

### **Foundry Services**

IceMOS Technology offers a wide range of additional processing services for customers who simply require a high-quality single unit process to be performed on their own wafers. IceMOS offers high resolution SAM (Scanning Acoustic Microscope) imaging of our bonded BSOI and CSOI wafers, this can also be offered as a service for customer's own bonded wafers. SAM inspection offers a means of nondestructive imaging of the bonded interface. In contrast to common non-destructive test methods such as conventional ultrasonic test methods, infrared microscopy and x-ray microscopy, Scanning Acoustic Microscopes scan the specimen surface pixel to pixel, line to line and detect with a special transducer the reflected ultrasonic waves out of the specimen. IceMOS SAM inspection offers a detection limit in the range of 10µm lateral size of delamination with a delaminated height in the range of 15nm. IceMOS can offer high resolution whole wafer scanning on wafer diameters 100mm – 200mm with a pixel size as small as 20  $\mu m.$  Individual areas of the wafer can be scanned at higher resolutions.

IceMOS Technology will use engineering expertise to develop a process flow and CAD (Computer Aided Design) layout used to develop a new set of masks or cross-sectional concept drawings.

The standards of IceMOS unit process foundry services are unsurpassed by any other foundry. With processes operated within an IATF 16949 manufacturing environment, controlled to tight tolerances by Statistical Process Control (SPC) and within contamination standards required by advanced CMOS, IceMOS offers you the perfect solution. All this is supported by a fast turnaround service and high compliance on On-Time-Delivery.

Cooler than Cool

https://www.icemostech.com/

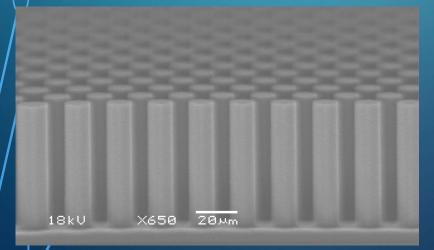

#### DRIE Etch Services

Deep trench etch is a core technology of IceMOS. With over 20 years' experience in this field, IceMOS Technology can offer DRIE Silicon etch options with minimum feature size 2um, on SOI up to 300um thick, trenches with aspect ratios of 20:1, large area patterns on SOI and Si wafers with exposed areas up to 65% and up to 500um through wafer etching on bulk Si and on SOI with aspect ratios up to 12:1. If required, our refill technology will not only ensure a completely filled trench, but will also leave a fully planar silicon surface for subsequent processing. Examples of just a small sample of what we can do are shown below. Contact our engineering team to discuss etch depth, sidewall angle, aspect ratio, exposed etch area and whether you require refill.

Neighbouring High and Low aspect ratio trenches in SOI without undercut.

Thin Film Depositions & Diffusion

Conformal Oxide & Poly refill in trenches etched in SOI.

Excellent process control and a suite of High temperature thermal oxidation and LPCVD TEOS oxide and LPCVD polysilicon allow IceMOS to offer excellent facilities for those wishing to refill etched features or deposit stacks of thermal or sacrificial oxide layers and heavily n++ doped or undoped LPCVD Polysilicon layers.

|   | Process                                           | Diameter                          | Min<br>Thickness | Max<br>Thicknes<br>s | Toleranc<br>e (+/-) | Notes                           |   |

|---|---------------------------------------------------|-----------------------------------|------------------|----------------------|---------------------|---------------------------------|---|

|   | Dry<br>Oxidation                                  | 100mm, 125mm,<br>150mm &<br>200mm | 24nm             | 200nm                | 15%                 |                                 |   |

| ( | Wet<br>Oxidation                                  | 100mm, 125mm,<br>150mm &<br>200mm | 100nm            | 6000nm               | 5%                  |                                 | ( |

| / | Undoped<br>LPCVD<br>Polysilicon                   | 100mm, 125mm<br>& 150mm           | 200nm            | 4500nm               | 10%                 | Per deposition                  | / |

|   | Heavily<br>doped<br>LPCVD<br>Polysilicon<br>(n++) | 100mm, 125mm<br>& 150mm           | 200nm            | 4500nm               | 10%                 | Per deposition                  |   |

|   | LPCVD TEOS                                        | 100mm, 125mm<br>& 150mm           | 200nm            | 1000nm               | 5%                  | Densification at 1050C optional |   |

IceMOS Technology is focused on establishing itself as a best-in-class provider of cost effective and high performance Super Junction MOSFETs, MEMS solutions, Advanced Engineering Substrates, SOI and Bonded Silicon Substrates.

Encompassing over twenty years of expertise, unsurpassed manufacturing skill and the latest developments in technology, IceMOS ensures that each customer receives outstanding service from the point of initial enquiry through to product delivery. Offering innovative product development, design and specialized services, the engineering team at IceMOS provides an array of technical support. Our team offer customers the opportunity to receive tailored solutions and unique services by delivering the latest innovations in the Semiconductor industry. IceMOS will work directly with the customer to develop a unique specialized product if this is not already on offer. It is with this, that IceMOS's product portfolio remains unrivaled.

Northern Ireland facotry

#### **SOI & SiSi Inventory**

IceMOS hold inventory of 100mm, 125mm, 150mm and 200mm Si-Si and SOI wafers.

Please check our inventory list at website by access right QR CODE.

The list contains all wafers that are currently available in inventory.

Lead time for inventory items is approximately 2~4 weeks from receipt of order. If you require further processing of any of these wafers, we will be happy to consider your request.

To receive a quote and make an order, contact our sales team via phone or

email:<u>sales@icemostech.com</u>

IceMOS SOI Sales Europe Name: Rami Zakaria Phone: +44 28 90 574700 Email: ramizakaria@icemostech.com

#### IceMOS America Sales

Name: Hugh Griffin Phone: +44 28 90 574700 Email: <u>hughgriffin@icemostech.com</u> IceMOS Japan Sales (ASIA) Name: Fumika Hidaka Phone: +81-90-8614-7889 Email: fumikakuramae@icemostech.com